Kennismaking met de CMOS 4000-familie

Oud, maar nog steeds populair

De reeds in 1968 door RCA geïntroduceerde logica van de 4000-familie is nog steeds uiterst populair onder elektronica hobbyisten. Eerste oorzaak van deze populariteit is het feit dat deze IC's, in tegenstelling tot de soortgenoten uit de TTL-familie, nog steeds zonder problemen door vrijwel iedere onderdelenleverancier uit voorraad en tegen een spotprijsje worden geleverd.

| |

| De eerste uitvoering van een CMOS-4000 IC van RCA. (© Wikimedia) |

Daarnaast spelen ook de zeer onkritische eigenschappen van deze schakelingen een belangrijke rol. Het voedingsbereik is groot en de stroomopname minimaal. Daardoor kunt u volstaan met eenvoudige voedingen en hebt u geen last van vervelende stoorpieken die door de schakelingen op de voedingslijn worden geïntroduceerd. De schakelingen vergen geen ingangsstroom en leveren uitgangssignalen waarmee u andere logica-families kunt aansturen of zonder probleem een transistor in verzadiging kunt sturen. De schakelniveau's op de ingangen liggen dicht tegen de massa en de voeding aan, zodat u geen speciale buffers nodig hebt om de schakelingen vanuit bijvoorbeeld de collector van een transistor aan te sturen.

Doordat de 4000-familie met veldeffect transistoren is samengesteld, is de werking echter absoluut niet te vergelijken met deze van de traditionele 7400-familie(s). De 7400-IC's worden gestuurd met stromen en leveren stromen op hun uitgangen. De 4000-IC's worden gestuurd met spanningen en leveren spanningen op hun uitgangen.

Algemene eigenschappen van de 4000-familie

De algemene kenmerken van de 4000- familie kunnen als volgt worden samengevat.

- De ingangsweerstand is vrijwel oneindig (typisch 109 tot 1012 Ω), zodat nagenoeg géén vermogen noodzakelijk is voor de sturing.

- Op het omschakelmoment na wordt vrijwel geen vermogen uit de voeding opgenomen.

- De schakelingen veroorzaken geringe verontreinigingen op de voedingsspanning.

- Het omschakelen van de uitgangen van 'L' naar 'H' en vice versa gebeurt bij de halve voedingsspanning, hetgeen de storingsongevoeligheid van de ingangen optimaliseert.

- De schakelingen hebben een zeer groot voedingsbereik. De hele familie werkt betrouwbaar tussen 3 V en 15 V, sommige schakelingen kunnen ingezet worden tot voedingsspanningen van 18 V tot 20 V.

- Het standaard spanningsverschil op de uitgangen tussen 'L' en 'H' in bijna gelijk aan de voedingsspanning. Hierdoor kunt u vanuit een uitgang rechtstreeks de basis van een transistor aansturen, zonder enig risico dat een 'L' op de uitgang de transistor toch nog open stuurt.

De 4000-series

De 4000-familie bestaat in feite uit een aantal series, waarvan de eigenschappen op bepaalde punten afwijken.

- De A-serie

Deze verouderde serie heeft een ongebufferde uitgangsstructuur. Dat wil zeggen dat de uitgangseigenschappen afhankelijk zijn van het logisch niveau op de uitgang. - De B-serie

Vrijwel alle fabrikanten leveren tegenwoordig hun schakelingen alleen in de B-serie. Deze IC's hebben een gebufferde uitgang, hetgeen wil zeggen dat de uitgangsstructuur volledig complementair is. Deze schakelingen hebben een zeer lage en constante uitgangsimpedantie en zo goed als een ideale transfer-karakteristiek. - De UB-serie

Van sommige schakelingen uit de B-serie worden, voor speciale toepassingen, ongebufferde versies geleverd. Deze IC's hebben het achtervoegsel UB achter het typenummer.

Eigenschappen van de B-serie

Inleiding

Omdat de ongebufferde A-versie niet meer verkrijgbaar is, worden alleen de specificaties van de gebufferde B-serie besproken.

Opbouw

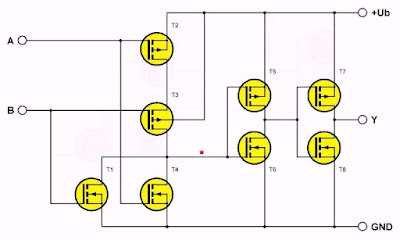

CMOS-schakeling bestaan, de naam zegt het reeds, alleen uit MOSFET transistoren. Door deze op een bepaalde manier in serie of parallel te schakelen ontstaan de gewenste logische functies. Als voorbeeld geeft de onderstaande figuur de typische samenstelling van een gebufferde NOR-poort met twee ingangen. De eigenlijke poort is opgebouwd uit de vier MOSFET-transistoren T1 tot en met T4, die in serie/parallel staan geschakeld. Afhankelijk van de spanningen op de twee ingangen gaan deze transistoren geleiden of sperren. Hun samenspel bepaalt de logische NOR-functie.

De vier overige transistoren T5 tot en met T8 vormen de volledig complementair samengestelde gebufferde eindtrap. Bij een ongebufferde versie van dit IC zouden deze vier transistoren niet aanwezig zijn en de uitgang van het IC rechtstreeks worden verbonden met de uitgang van de poortfunctie, aangegeven met een sterretje.

|

| Het intern schema van een gebufferde NOR-poort. (© 2023 Jos Verstraten) |

Voedingsspanning

Alle gebufferde typen van alle fabrikanten worden gegarandeerd over een voedingsspanningsbereik van 3 V tot 15 V. Sommige fabrikanten, zoals Philips, garandeerden een goede werking tot 18 V. De doorslagspanning van de interne transistoren ligt echter bij 20 V, zodat u bij gebruik van 18 V maar heel weinig veilige reserve hebt. Vandaar dat wordt aanbevolen CMOS-schakelingen te voeden met maximaal 15 V. Voeding uit de standaard 5 V voeding van TTL is dus zonder meer mogelijk. Wel is het zo dat de schakeleigenschappen van de IC's slechter worden als de voedingsspanning daalt. De schakeltijden nemen namelijk toe bij dalende voedingsspanning.

Vermogensverbruik

Onder statische omstandigheden, dus een poort met stabiele niveau's op in- en uitgangen, zal het nooit voorkomen dat de P-kanaal en de N-kanaal transistoren gelijktijdig geleiden. Er vloeit dan geen actieve stroom door de schakeling en de enige stroom die uit de voeding wordt opgenomen is de som van alle lekstromen van alle transistoren. Deze lekstroom bedraagt bij moderne serie's, zoals de LOCMOS-serie van Philips, typisch 0,5 nA per poort. Bij een voedingsspanning van 5 V levert deze stroom een vermogensverbruik op van slechts 2,5 nW (!!) per poort.

Het stroomverbruik stijgt uiteraard als de poort actief wordt en de diverse transistoren omschakelen van sper naar geleiding en vice versa. Er moeten dan een heleboel parasitaire capaciteiten geladen en ontladen worden, hetgeen zich uiteraard uit onder de vorm van een stroomopname. Bovendien zullen de P- en N-kanaal transistoren, bij het omschakelen van toestand, even samen door hun geleidingsgebied lopen, waardoor er een stroompiekje van de voeding wordt gevraagd. Het actieve stroomverbruik (en dus het vermogensverbruik) is afhankelijk van de frequentie waarmee de schakelingen geactiveerd worden.

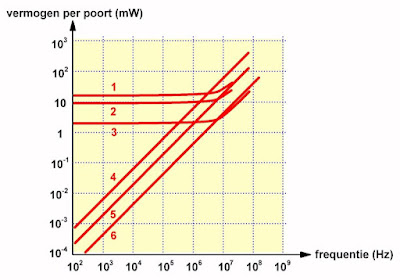

In de onderstaande figuur is een grafiekje getekend waarin het verband wordt gegeven tussen de schakelfrequentie en het vermogensverbruik per poort. Hieruit blijkt dat CMOS-schakelingen veel zuiniger zijn dan TTL-IC's bij frequenties onder 1 MHz. Boven deze frequentie wordt het vermogensverbruik vergelijkbaar. Let op het feit dat de vermogens-as een logaritmische indeling heeft en dat iedere schaalverdeling overeen komt met een factor 10 meer of minder vermogen! De cijfers in de grafiek staan voor:

- 1: Schottky TTL

- 2: standaard TTL

- 3: Low power TTL

- 4: CMOS bij 15 V

- 5: CMOS bij 10 V

- 6: CMOS bij 5 V

|

| Vergelijking van het vermogensverbruik. (© 2023 Jos Verstraten) |

De poortvertraging

Als u aan de ingang van een CMOS-inverter een smalle stijgende puls legt zal de schakeling deze puls inverteren en ontstaat er aan de uitgang een dalende puls. Niets werkt traagheidsloos en vandaar dat er een vertraging aanwezig is tussen het aanleggen van de puls op de ingang en het verschijnen van een puls op de uitgang. Deze vertraging noemt men de 'poortvertraging' of de 'propagation delay'. In de onderstaande geïdealiseerde grafiek is weergegeven hoe men deze vertraging definieert. De tpHL en de tpLH zijn de tijden die verlopen tussen het moment dat de ingangsspanning gelijk wordt aan de helft van de voedingsspanning en het moment dat de uitgangsspanning gelijk wordt aan deze waarde. Vanwege de volledig symmetrische opbouw van een type-B CMOS-uitgang zijn deze tijden aan elkaar gelijk.

|

| Definitie van de poortvertraging. (© 2023 Jos Verstraten) |

Poortvertragingen vergelijken

Tóch komen de modernste series, zoals LOCMOS van Philips, een aardig eind! In de onderstaande figuur wordt de vertraging over één poort van standaard CMOS, LOCMOS en TTL met elkaar vergeleken. Uit deze grafieken blijkt duidelijk dat de vertraging van CMOS-schakeling erg afhankelijk is van de capaciteit, die op een uitgang is aangesloten. Bij kleine belastingscapaciteiten lopen de vertragingen niet erg uit elkaar. Neemt de capacitieve belasting toe, dan gaat de poortvertraging van CMOS vrij snel stijgen.

Dat is vrij logisch, want de gebufferde CMOS-schakelingen hebben, vergeleken met TTL-schakelingen, een vrij hoge uitgangsimpedantie. Een typische TTL-poort heeft bijvoorbeeld een uitgangsimpedantie van 25 Ω in de 'L'-stand. Dezelfde grootheid voor een CMOS-poort heeft een waarde van 250 Ω. De uitgangsimpedantie vormt, samen met de belastingscapaciteit, een laagdoorlaat filtertje, dat verantwoordelijk is voor het snel stijgen van de poortvertraging.

|

| Vergelijking van de poortvertragingen. (© 2023 Jos Verstraten) |

Poortvertraging in functie van de voedingsspanning

Een grafiek zoals de bovenstaande geeft een goed vergelijkend inzicht, maar geeft geen absolute vertragingswaarden. Die worden wél geleverd door de onderstaande grafiek. Hierin wordt de numerieke vertraging van een LOCMOS-poort uitgezet in functie van de capacitieve belasting op de uitgang van de poort, met de voedingsspanning als parameter.

Uit deze grafiek blijkt duidelijk hoe groot de invloed van de voedingsspanning is op de poortvertraging. Hoe hoger de voedingsspanning is, hoe sneller CMOS werkt!

Ook de temperatuur van de chip heeft invloed op de snelheid waarmee CMOS werkt. In het algemeen kunt u stellen dat de snelheid daalt als de chip warmer wordt. Dit verschijnsel wordt veroorzaakt door het feit dat de mobiliteit, waarmee de ladingsdragers vanuit en naar de gates van de transistoren migreren, wordt beïnvloed door de temperatuur.

|

Numerieke waarden van de poortvertragingen. |

Storingsongevoeligheid

Met storingsongevoeligheid van digitale schakelingen wordt aangegeven hoe groot het verschil is tussen de minimale en maximale spanningen die door de schakelingen als 'L' en als 'H' worden geïnterpreteerd. Hoe groter deze spanningsverschillen, hoe storingsongevoeliger de logica. Een van de grote voordelen van CMOS is dat deze technologie zeer ongevoelig is voor dergelijke storingen. De omschakeldrempel van een CMOS-poort, dat is de spanning op de ingang waarbij de uitgang van de poort omschakelt van 'L' naar 'H' of vice versa, ligt ongeveer in het midden van de voedingsspanning. Voedt u dus CMOS-schakelingen met 15 V, dan ligt deze drempel bij 7,5 V. Omdat de standaard spanningsniveau's van 'L' en 'H' ver uit de buurt van deze drempel liggen, zal een CMOS-poort nooit per ongeluk een 'L'-signaal als 'H' interpreteren of omgekeerd.

Het spanningsverschil tussen de maximale waarde van een 'L' en de minimale waarde van een 'H' is zeer groot:

- 2,25 V bij 5 V voedingsspanning.

- 4,50 V bij 10 V voedingsspanning.

- 6,75 V bij 15 V voedingsspanning.

Vergeleken met de vaak maar 1 V bij standaard-TTL zit u wat dit betreft bij CMOS dus wel heel goed!

In een CMOS-systeem, gevoed op 5 V, kan de voedingsspanning zonder problemen korte spanningsdalingen (stoorpieken) van meer dan 1 V vertonen, zonder dat de logica daar last van heeft. Hetzelfde geldt voor het massa-niveau. Bij TTL-systemen zouden dergelijke pieken op de massa of op de voeding onverbiddelijk grote problemen veroorzaken.

Waar u bij het ontwerpen van CMOS-schakelingen echter wél goed rekening mee moet houden is de hoge uitgangsimpedantie van de uitgangen. Een gevolg is dat de schakelingen vrij gevoelig zijn voor capacitieve belastingen.

Beveiliging van de ingangen

De ingang van een CMOS-poort lijkt voor de op de ingang aangesloten schakeling op een kleine condensator. Gemiddelde waarde: 1 pF, lekstroom naar de massa: 1 pA. Het zal duidelijk zijn dat een dergelijke ingang heel gevoelig is voor statische elektriciteit. Zonder speciale beveiligingsmaatregelen zou de ingang van een CMOS-IC al beschadigd kunnen worden door het simpelweg aanraken van een van de pennetjes. Het menselijk lichaam zit immers vol statische elektriciteit, die ontstaat door wrijving tussen kleding.

Vandaar dat alle fabrikanten van CMOS-schakelingen een aantal maatregelen hebben getroffen om hun schakelingen te beveiligen tegen statische ladingen. De interne beveiliging van een standaard CMOS-IC is getekend in de onderstaande figuur.

|

| Beveiliging op de in- en uitgangen van een CMOS-schakeling. (© 2023 Jos Verstraten) |

De beveiligingen bestaan uit R/D-netwerkjes, die alle in- en uitgangen beschermen. De weerstanden hebben een typische waarde van 400 Ω en de dioden een doorslagspanning van ongeveer 20 V.

Deze interne beveiligingen hebben een aantal consequenties, waar u bij het werken met CMOS heel goed rekening mee moet houden!

- Het is absoluut verboden een CMOS-IC verkeerd om met de voedingsspanning te verbinden. Het zal duidelijk zijn dat de in serie geschakelde dioden dan onmiddellijk gaan geleiden en vernietigd worden.

- De maximale stroom door de beveiligingsdioden bedraagt 10 mA. Het is dus verboden ingangsspanningen aan te leggen die 4 V positiever zijn dan de voedingsspanning of 4 V negatiever dan het massa-potentiaal. In beide gevallen zal er namelijk meer dan 10 mA door een van de beveiligingsdioden gaan vloeien.

- Het is verboden spanningen op de ingangen te zetten als de schakelingen niet met de voeding verbonden zijn. Ook in dat geval gaan de dioden immers geleiden en zal de stroom groter worden dan 10 mA.

- Niet gebruikte ingangen mogen, dit in tegenstelling tot de TTL-praktijk, nooit open gelaten worden. De beveiligingsdioden hebben uiteraard een lekstroom en deze stroom zal er voor zorgen dat op een niet aangesloten ingang een bepaalde spanning komt te staan, met een ongedefinieerde waarde ergens tussen massa en voeding. Een dergelijke spanning zal door de schakeling als 'L' of 'H' worden geïnterpreteerd, afhankelijk van de parameters van de individuele schakeling. Niet gebruikte ingangen moet u dus altijd met de massa ('L') of met de voeding ('H') verbinden.

Uitgangskarakteristieken

De fan-out van CMOS-schakelingen onderling kent geen grenzen. Vanwege de zeer hoogimpedante ingangen kunt u in theorie een oneindig aantal ingangen met één uitgang verbinden. Natuurlijk speelt hierbij de capacitieve belasting een rol en vandaar dat men in de praktijk stelt dat één CMOS-uitgang maximaal 40 CMOS-ingangen mag aansturen.

Bij een voedingsspanning van 5 V is de maximale spanning van een 'L' op een uitgang gelijk aan 1,5 V en de minimale spanning van een 'H' op de uitgang 3,5 V. De typische waarden voor deze spanningen bedragen 0,05 V en 4,95 V. De te verwachten logische spanningen zitten dus vrijwel op de waarde van het massa-potentiaal en de voeding! Hieruit volgt dat de door CMOS geleverde logische signalen zonder enig probleem door TTL als dusdanig worden herkend. Toch zijn er wat problemen bij het interfacen van CMOS met TTL. Hierover meer in het volgens hoofdstuk.

CMOS naar TTL interfacing

Inleiding

Vaak zult u in de praktijk in één schakeling zowel TTL- en CMOS-IC's gebruiken. Dan doet zich het probleem voor hoe de in- en uitgangen van deze twee zeer verschillende technologieën op elkaar aangesloten moeten worden. Het grote probleem is dat TTL met stroomsturing werkt en CMOS met spanningssturing. Een tweede probleem is dat de gegarandeerde spanningsdrempels voor 'L' en voor 'H', bij een voedingsspanning van 5 V, nogal uit elkaar lopen. Dit wordt voorgesteld in de onderstaande figuur. Hieruit blijkt dat de minimale 'H'-waarde van TTL, 2,4 V, lager is dan de minimaal als 'H' verwachte drempel van 3,5 V bij CMOS. Hier kunnen dus problemen ontstaan! Een hoge TTL-uitgang kan dus niet als dusdanig door CMOS worden geïntepreteerd. Omgekeerd zijn er geen problemen. Zowel de maximale waarde van 'L' als de minimale waarde van 'H' van CMOS voldoen aan de TTL-eisen.

|

| De logische niveaus van TTL en CMOS. (© 2023 Jos Verstraten) |

Interfacing van TTL naar CMOS, 5 V voeding

Het probleem van de te lage 'H'-waarde van TTL is gemakkelijk op te lossen volgens de onderstaande figuur. De uitgang van de TTL-poort wordt via een optrek-weerstand Rx verbonden met de 5 V voedingsspanning. Deze weerstand zorgt ervoor dat de minimale 'H'-waarde van 2,4 V wordt opgetrokken tot minstens 3,5 V.De waarde van de weerstand Rx is afhankelijk van het type TTL-schakeling die u op de CMOS-ingang aansluit:

- Standaard 74: minimaal 390 Ω, maximaal 4,7 kΩ

- 74H: minimaal 270 Ω, maximaal 4,7 kΩ

- 74L: minimaal 1,5 kΩ, maximaal 27 kΩ

- 74LS: minimaal 820 Ω, maximaal 12 kΩ

- 74S: minimaal 270 Ω, maximaal 4,7 kΩ

|

Interfacing van TTL naar CMOS, 5 V voeding. |

Interfacing van TTL naar CMOS, verschillende voedingsspanningen

Als het TTL-deel van uw schakeling uit 5 V wordt gevoed en het CMOS-deel uit een hogere spanning moet u het schema van de onderstaande figuur toepassen. De interface bestaat nu uit een TTL-buffer met verhoogde spanningsgrenzen en open-collector uitgangen, zoals de 7416. De uitgangen van deze buffer worden via een belastingsweerstand Rx verbonden met de voedingsspanning van de CMOS-schakelingen. Bij een CMOS-voeding van 10 V kunnen de weerstanden een waarde van 39 kΩ hebben.

|

| Interfacing van TTL naar CMOS, verschillende voeding (1). (© 2023 Jos Verstraten) |

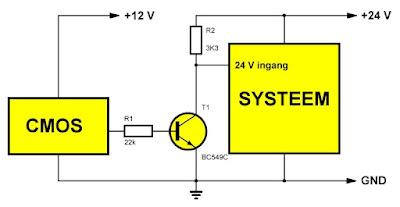

TTL-IC's zijn echter nogal uit de gratie en de kans dat u zo'n speciale buffer als de 7416 vindt bij uw reguliere onderdelenleverancier is niet zo groot. Als de schakeling die u ontwerpt geen snelle pulsen moet verwerken kunt u natuurlijk ook een transistortrapje tussenschakelen volgens het onderstaand schema. Denk er aan dat ook deze trap inverterend werkt!

|

Interfacing van TTL naar CMOS, verschillende voeding (2). |

Van CMOS naar TTL, 5 V voeding

Het probleem is dat de CMOS-uitgang een stroom uit de TTL-ingang moet kunnen opnemen, waarbij de op de uitgang opgebouwde spanning niet groter mag worden dan 0,4 V. Nu heeft een standaard CMOS-uitgang een vrij hoge uitgangsimpedantie en het gevolg is dat de kans groot is dat de stroom van 1,6 mA die door de TIL-ingang geleverd wordt, een te grote spanning opbouwt. Vandaar dat in ieder geval wordt aanbevolen een speciale buffer tussen te schakelen, zoals de 4049 of 4050. Het schema is getekend in de onderstaande figuur. Maar ook de speciale buffers hebben een beperkte aansturingscapaciteit! De uitgang van een buffer uit een 4049 of 4050 kan maximaal het onderstaand aantal TTL-ingangen aansturen:

- standaard 74: typisch 3 uitgangen, in ieder geval 1 uitgang

- 74H: typisch 2 uitgangen, in ieder geval 1 uitgang

- 74L: typisch 28 uitgangen, in ieder geval 14 uitgangen

- 74LS: typisch 14 uitgangen, in ieder geval 7 uitgangen

- 74S: typisch 2 uitgangen, in ieder geval 1 uitgang

|

Interfacing van CMOS naar TTL, 5 V voeding. |

CMOS-interfacing naar de buitenwereld

Inleiding

Vaak moet u op de ingang van een CMOS-schakeling een signaal aansluiten dat afkomstig is van de buitenwereld, bijvoorbeeld een analoog stuursignaal. Even zo vaak moet u vanuit de uitgang van een CMOS-poort een analoge schakeling aansturen. Ook voor deze interfacing bestaan bepaalde eenvoudige regeltjes, die tot slot van dit artikel in het kort worden toegelicht.

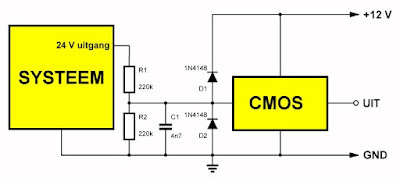

Aansturen van CMOS-ingangen

Vanwege de gevoeligheid van CMOS-ingangen voor te hoge of te lage spanningen moet u, ondanks de interne beveiligingen in het IC, tussen een analoge uitgang en een CMOS-ingang een extra beveiliging opnemen. Een typische schakeling is getekend in de onderstaande figuur. In dit geval moet een signaal met een maximale amplitude van 24 V worden verbonden met de ingang van een CMOS-poort. De CMOS-schakeling wordt gevoed uit 12 V. Een resistieve spanningsdeler R1-R2 zorgt voor het reduceren van de maximale ingangsspanning tot 12 V. Over de onderste weerstand staat een condensator C1 geschakeld die gebruikt wordt voor het onderdrukken van smalle stoorpulsjes op het ingangssignaal. Nadien volgen nog eens twee siliciumdioden D1 en D2, die de ingang van de poort beschermen tegen verkeerd-om gepolariseerde spanningen. Weliswaar heeft de ingang van het CMOS-IC al twee van dergelijke dioden ingebouwd, maar in het ergste geval is het uiteraard goedkoper om een externe diode te vervangen dan een heel IC.

|

| Aansluiten van een hoge spanning op de ingang van een CMOS-IC. (1) (© 2023 Jos Verstraten) |

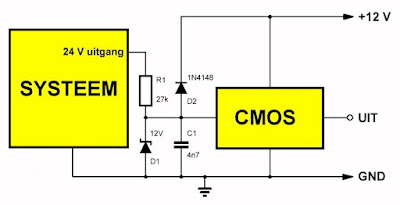

Een tweede bruikbaar systeem is getekend in de onderstaande figuur. Hier wordt de te hoge ingangsspanning gereduceerd door het toepassen van een zenerdiode. Hiermee wordt één onderdeel uitgespaard, omdat nu uiteraard een van de twee silicium-dioden kan vervallen.

|

Aansluiten van een hoge spanning op de ingang van een CMOS-IC. (2) |

Het uitsturen van CMOS-schakelingen

Vanwege de hoge uitgangsimpedantie kan een CMOS-schakeling niet erg veel belastingsstroom aan een externe schakeling leveren. U doet er verstandig aan in ieder geval een schakeltransistor tussen te schakelen. Het standaard schema is getekend in de onderstaande figuur. De CMOS-poort stuurt via een weerstand R1 van 22 kΩ een transistor in verzadiging. U kunt de uitgangsspanning van de collector aftakken en gebruiken voor het besturen van externe processen.

|

| Van een CMOS-uitgang naar de buitenwereld. (© 2023 Jos Verstraten) |

Op-amp's en CMOS

Uitgangsspanningen van operationele versterkers kunnen vrij eenvoudig worden gebruikt voor het aansturen van de ingang van een CMOS-schakeling. Neem als voorbeeld een operationele versterker die is geschakeld als inverterende versterker met een versterkingsfactor van -10. De niet-inverterende ingang van de schakeling wordt door middel van een spanningsdeler ingesteld op de helft van de voedingsspanning.

De uitgang van de operationele versterker kan in principe rechtstreeks op de ingang van een CMOS-poort worden aangesloten. In de meeste gevallen zal echter het uitgangssignaal van een operationele versterker te traag variëren. Hierdoor bevinden de voor- en achterflank van het op-amp signaal zich een tijdje tussen de 'L'- en 'H'-drempels van de CMOS-poort. Er kunnen dan allerlei ongewenste en niet te voorspellen stoorsignalen op de uitgang van de poort ontstaan. Om dit te voorkomen is het aan te raden dat u een CMOS schmitt-trigger, bijvoorbeeld een 4093, tussen de uitgang van de op-amp en de ingang van de CMOS-poort opneemt. Het basisschema is voorgesteld in de onderstaande figuur.

|

| Interfacing tussen een op-amp en een CMOS-IC. (© 2023 Jos Verstraten) |

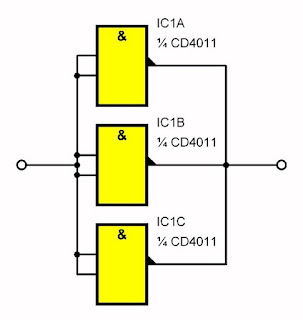

Het parallel schakelen van de in- en uitgangen van TTL-schakelingen is absoluut verboden. Bij CMOS kan dit zonder problemen, onder voorwaarde dat u dit grapje alleen uithaalt bij identieke poorten die in een en dezelfde behuizing zitten. Zo kunt u, om de stroomcapaciteit van de uitgang te verdrievoudigen, volgens het onderstaand schema drie CMOS-NAND's parallel schakelen. Op deze manier kunt u, als u in een behuizing een of meerdere poorten over hebt, deze parallel schakelen om de extra transistor in de uitgang uit te sparen. Deze oplossing is natuurlijk alleen bruikbaar als de uitgangsspanning niet groter hoeft te zijn dan de voedingsspanning van de CMOS-schakeling.

|

| Parallel schakelen van identieke poorten uit één behuizing. (© 2023 Jos Verstraten) |

Het aansturen van LED's

Vaak komt het voor dat u de logische toestand op de uitgang van een poort moet aangeven door middel van een LED. Bij TTL-schakelingen kunt u een LED, via een serieweerstand, rechtstreeks aansluiten op de uitgang van de poort. Bij CMOS kan dat alleen als u gevoelige miniatuur LED's met een grote lichtopbrengst gebruikt, die dus ook bij minimale stroom veel licht uitstralen. Moet u normale 5 mm LED's toepassen, dan moet u een buffer toepassen, volgens het onderstaand schema. De CD4050 is een niet-inverterende buffer die in staat is voldoende stroom te leveren voor het laten branden van dergelijke vrij ongevoelige LED's. Natuurlijk kunt u ook gebruik maken van een schakeltransistor.

|

| Aansturen van een ongevoelige LED. (© 2023 Jos Verstraten) |

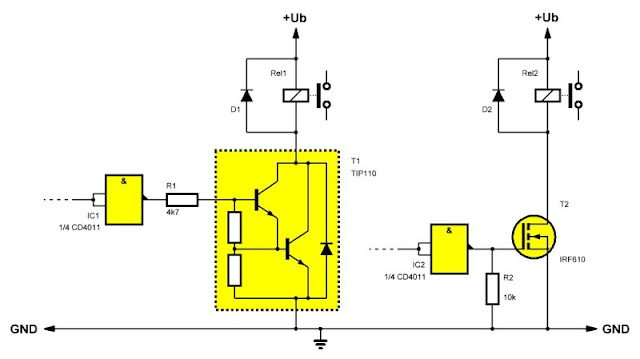

Het aansturen van zware belastingen

Moet u uit een CMOS-uitgang een zware belasting aansturen, bijvoorbeeld een heel zwaar industrieel relais, dan is ook een enkelvoudige transistortrap niet in staat de noodzakelijke stroom te leveren. Het ligt voor de hand gebruik te maken van een darlington, zoals links voorgesteld in de onderstaande figuur. Een goedkoop type is de TIP110. De waarde van de basisweerstand R1 is afhankelijk van de voedingsspanning van de CMOS-schakeling:

- Voedingsspanning 5 V: weerstand R1 = 1 kΩ

- Voedingsspanning 10 V: weerstand R1 = 4,7 kΩ

- Voedingsspanning 15 V: weerstand R = 8,2 kΩ

Uiteraard kunt u ook een N-channel enhancement MOSFET toepassen, deze zijn tegenwoordig vaak goedkoper te verkrijgen dan darlingtons en hebben een veel lagere AAN-weerstand. Bruikbare types zijn onder andere de IRF610 en de IRFZ44N.

|

| Aansturen van een zwaar relais. (© 2023 Jos Verstraten) |